Definition

Pipelined Processor

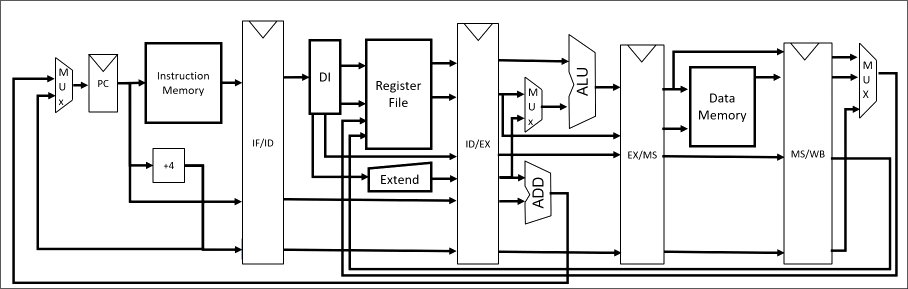

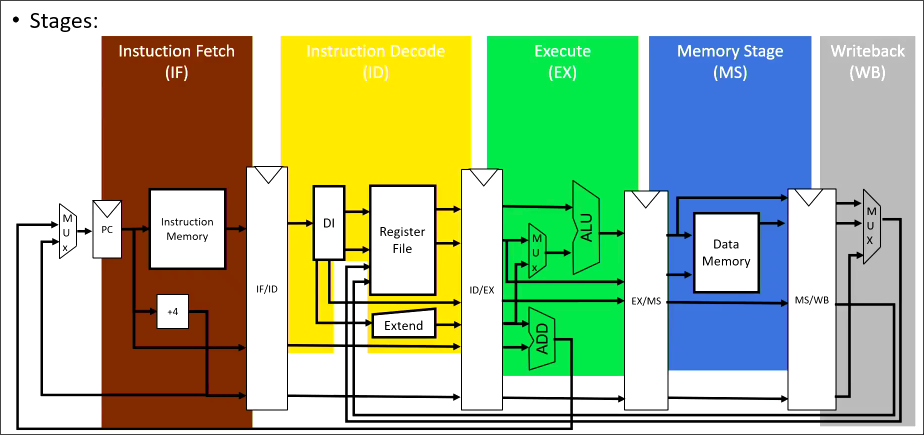

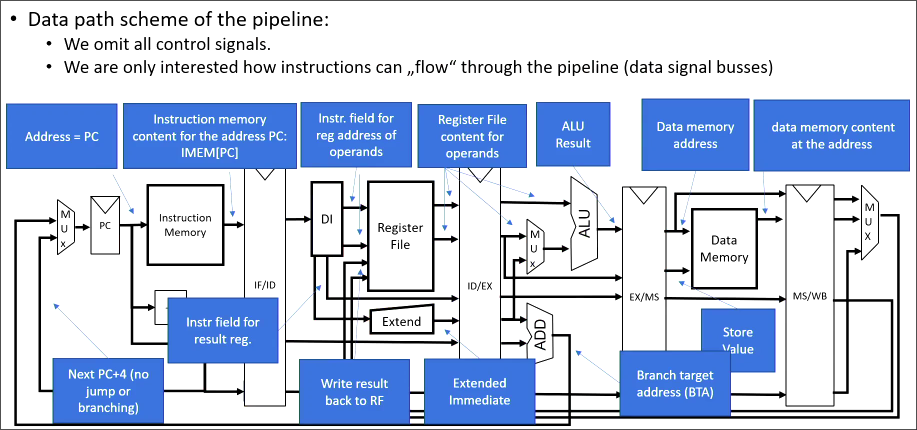

A pipelined processor is a processor whose instruction processing is divided into stages, so that several instructions can be in different stages at the same time.

Instead of waiting for one instruction to finish completely before starting the next, the processor overlaps their execution. This is a form of temporal parallelism.

Typical stages are fetch, decode, execute, memory access, and write-back.

Effect

Throughput

A pipelined processor mainly improves throughput rather than the latency of a single instruction.

Each instruction still passes through all stages, but once the pipeline is full, several instructions make progress in parallel.

Example

Overlapped instruction execution

In one clock cycle, one instruction may be decoded while an earlier instruction is executed and an even earlier instruction writes back its result.

So multiple instructions are active at once, but each one is in a different stage of the pipeline.

The following timeline contrasts a single-cycle design with a pipelined one.

Example