Definition

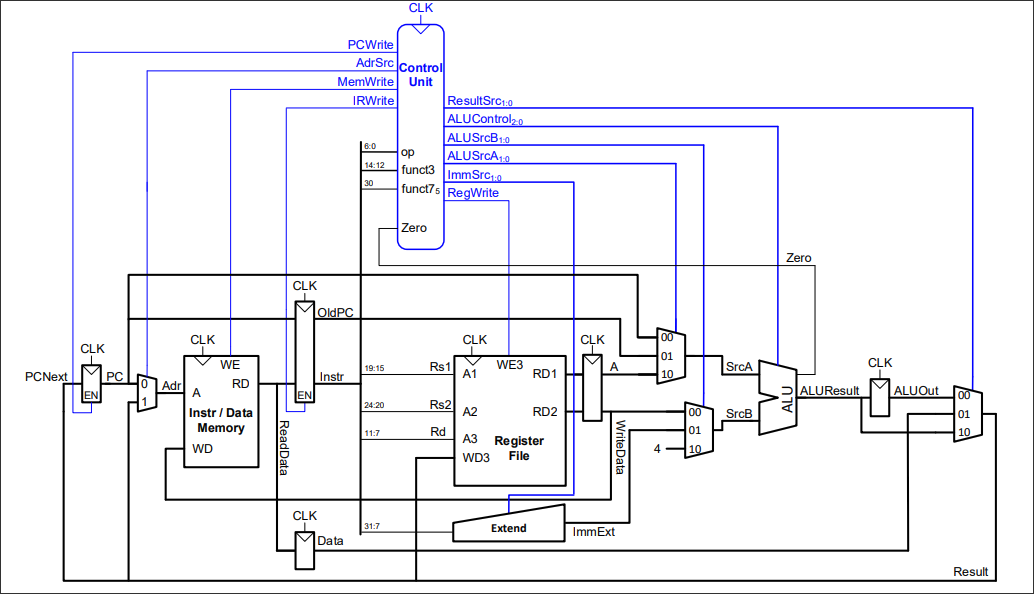

Multi-Cycle Processor (RISC-V)

A multi-cycle processor for RISC-V is a microarchitecture in which one instruction is executed over several clock cycles.

The work of an instruction is split into shorter phases, such as fetch, decode, execute, memory access, and write-back. Different instructions may therefore require different numbers of cycles.

Compared with a single-cycle processor, this allows the processor to use shorter cycles and to reuse hardware across several cycles.

Comparison

Single-cycle vs multi-cycle

A single-cycle processor is simple, but its clock period is limited by the longest instruction, typically lw. Since all work must happen in one cycle, it also needs more hardware in parallel, such as separate instruction and data memories and several adders or ALUs.

A multi-cycle processor addresses these problems by breaking instruction execution into shorter steps.

This gives three main advantages:

- the clock period can be shorter, so the clock speed can be higher;

- simpler instructions can finish in fewer cycles than more complex ones;

- expensive hardware can be reused across cycles instead of being duplicated.

The main disadvantage is repeated sequencing overhead. The control unit must manage several steps per instruction, and this overhead is paid in multiple cycles.

Phases

Typical instruction phases

A multi-cycle processor usually splits instruction execution into a small sequence of phases.

Not every instruction uses all phases. For example, an arithmetic instruction has no data-memory phase, while a store instruction has no write-back phase.

Design

The design process is the same as for the single-cycle processor:

- first construct the datapath;

- then derive the control.

Examples

Example